1. Tujuan [back]

- Mengetahui bentuk rangkaian ripple asynchronous counter

-Memahami prinsip kerja rangkaian ripple asynchronous counter

2. Alat dan Bahan [back]

3. Dasar Teori

[back]-Memahami prinsip kerja rangkaian ripple asynchronous counter

2. Alat dan Bahan [back]

- JK Flip - Flop

- Clock

- Logic State

- Logic Probe

Komponen yang dibutuhkan:

- JK Flip - Flop

J dan K disebut masukan pengendali karena menentukan apa yang dilakukan oleh flip-flop pada saat suatu pinggiran pulsa positif diberikan. Rangkaian RC mempunyai tetapan waktu yang sangat pendek, hal ini mengubah pulsa lonceng segiempat menjadi impuls sempit. Pada saat J dan K keduanya 0, Q tetap pada nilai terakhirnya. Pada saat J rendah dan K tinggi, gerbang atas tertutup, maka tidak terdapat kemungkinan untuk mengeset flip-flop. Pada saat Q adalah tinggi, gerbang bawah melewatkan pemicu reset segera setelah pinggiran pulsa lonceng positif berikutnya tiba. Hal ini mendorong Q menjadi rendah . Oleh karenanya J = 0 dan K=1 berarti bahwa pinggiran pulsa lonceng positif berikutnya akan mereset flip-flopnya. Pada saat J tinggi dan K rendah, gerbang bawah tertutup dan pada saat J dan K keduanya tinggi, kita dapat mengeset atau mereset flip-flopnya. Untuk lebih jelasnya daat dilihat pada tabel kebenaran JK flip-flop berikut.

- Clock

Clock merupakan sinyal listrik yang berupa suatu denyutan dan berfungsi untuk mengkoordinasikan atau mengsinkronisasikan setiap aksi2x atau proses2x yg dilakukan oleh setiap komponen didalam perangkat elektronika.

- Logic State

Untuk memberikan input 1 atau 0 pada rangkaian

- Logic Probe

Untuk menampilkan logika hasil dari rangkaian

11.1 Ripple Asynchronous Counter

Merupakan sebuah penghitung riak adalah susunan aliran dari flip-flop

dimana output dari satu flip-flop mengatur input clock dari flip-flop selanjutnya.

Jumlah flip – flop didalam rangkaian riak tergantung pada jumlah logic state

yang berbeda - beda yang dilaluinya

sebelum mengulangi urutan, parameter nya dikenal sebagai modulus counter. Dalam

penghitung riak, yang juga biasa disebut asynchronous counter atau serial

counter, input clock digunakan hanya untuk flip – flop yang pertama, yang juga

disebut input flip – flop, dalam susunan rangkaian. Clock input ke flip – flop selanjutnya

berasal dari output flip – flop sebelumnya. Singkatnya, output dari flip – flop

pertama berperan sebagai input flip – flop kedua, dan output dari flip – flop kedua

memberikan clock input untuk flip – flop ketiga, dan seterusnya. Dalam susunan

n flip-flop, clock input ke flip-flop ke-n berasal dari output flip-flop (n −

1) untuk n> 1.

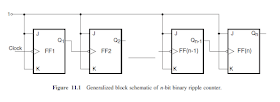

Gambar 11.1 menunjukkan susunan skematis blok umum dari

penghitung riak biner n-bit.

Sebagai konsekuensi alaminya, tidak semua flip – flop logikanya

berubah pada saat yang sama. Flip-flop yang kedua dapat mengubah logika hanya

setelah output flip-flop pertama telah mengubah logikanya. Oleh karena itu, logika flip-flop yang kedua akan berubah dengan waktu delay tertentu setelah terjadinya pulsa clock input karena

fakta bahwa ia mendapat input clock sendiri dari output flip-flop pertama dan

bukan dari clock input. Waktu tunda ini di sini sama dengan jumlah

keterlambatan perambatan dari dua flip - flop, yang pertama dan yang jepit

kedua. Secara umum, flip-flop ke-n akan berubah status hanya setelah delay

tersebut sama dengan n kali delay perambatan dari satu flip-flop. Istilah 'penghitung

riak' berasal dari mode in dimana informasi clock beriak melalui konter. Ini

juga disebut 'Asynchronous Counter' karena flip – flop yang berbeda yang

terdiri atas penghitung, logikanya tidak berubah dalam sinkronisasi dengan clock

input. Dalam counter, setelah terjadinya setiap pulsa input clock, penghitung

harus menunggu jangka waktu yang sama dengan jumlah penundaan perambatan dari

semua flip - flop sebelum pulsa clock berikutnya dapat digunakan. Penundaan perambatan

dari setiap flip-flop, tentu saja, akan tergantung pada logika dimana ia berada

Penundaan Perambatan di Penghitung Riak

Masalah utama dengan penghitung riak muncul dari

keterlambatan perambatan flip - flop yang merupakan counter. Seperti disebutkan

dalam paragraf sebelumnya, keterlambatan perambatan yang efektif dalam ripple

counter sama dengan jumlah keterlambatan perambatan karena flip-flop yang

berbeda. Situasi menjadi lebih buruk dengan peningkatan jumlah flip – flop yang

digunakan untuk merangkai penghitung, yang merupakan kasus yang lebih besar

dalam penghitung bit. Kembali ke penghitung riak, peningkatan keterlambatan perambata

membatasi frekuensi maksimum yang digunakan sebagai clock input ke counter. Kita

dapat apresiasi bahwa periode waktu sinyal clock harus sama dengan atau lebih

besar dari total keterlambatan perambatan. Oleh karena itu, frekuensi clock

maksimum itu sesuai dengan periode waktu

yang sama dengan total keterlambatan perambatan. Jika tpd adalah keterlambatan

perambatan di setiap flip-flop, kemudian, dalam sebuah counter dengan

N-flip-flop memiliki modulus kurang dari atau sama dengan 2N, frekuensi clock

maksimum yang dapat digunakan didapatkan dari

fmax= 1 / (N × tpd).

Seringkali, dua waktu

tunda perambatan ditentukan dalam kasus flip - flop, satu untuk transisi

LOW-to-HIGH (tpLH) dan yang lainnya untuk transisi TINGGI ke RENDAH (tpHL) pada

output. Dalam kasus seperti itu, yang lebih besar dari keduanya harus dipertimbangkan

untuk menghitung frekuensi clock maksimum. Sebagai contoh, dalam kasus counter

riak IC milik Schottky TTL berdaya rendah (LSTTL) , penundaan perambatan per

flip-flop biasanya adalah urutan 25 ns. Ini menyiratkan bahwa penghitung riak

empat-bit dari jenis ini tidak dapat clock lebih cepat dari 10 MHz. Batas atas

pada frekuensi clock semakin berkurang dengan bertambahnya jumlah bit yang

harus ditangani oleh counter.

Penghitung Sinkron

Dalam penghitung sinkron, juga

dikenal sebagai penghitung paralel, semua flip-flop dalam penghitung berubah logika

pada saat yang sama dalam sinkronisme dengan sinyal input clock. Sinyal clock

dalam kasus ini adalah secara bersamaan diterapkan pada input clock dari semua

sandal flip-flop. Penundaan yang terlibat dalam kasus ini sama untuk penundaan perambatan

dari satu flip-flop saja, terlepas dari jumlah flip-flop yang digunakan untuk

membuat counter. Dengan kata lain, penundaan tidak tergantung pada ukuran

penghitung.

Modulus Penghitung

Modulus (nomor MOD) dari counter adalah

jumlah keadaan logika yang berbeda yang dilaluinya sebelumnya hingga kembali ke

keadaan awal untuk mengulangi urutan penghitungan. Penghitung n-bit yang

diperhitungkan semua keadaan logika sebenarnya dan tidak melewatkan satupun

logika memiliki modulus 2n. Kita bisa melihat counter memiliki modulus yang

merupakan kekuatan integral dari 2, yaitu, 2, 4, 8, 16 dan seterusnya. Ini bisa

saja dimodifikasi dengan bantuan logika kombinasional tambahan untuk

mendapatkan modulus kurang dari 2n.

Untuk menentukan jumlah flip-flop

yang diperlukan untuk membangun penghitung yang memiliki modulus tertentu,

identifikasi bilangan bulat terkecil m yang sama dengan atau lebih besar dari

modulus yang diinginkan dan juga sama untuk kekuatan integral 2. Misalnya, jika

modulus yang diinginkan adalah 10, yang merupakan kasus dalam satu decade counter,

bilangan bulat terkecil lebih besar dari atau sama dengan 10 dan yang juga

merupakan kekuatan integral dari 2 adalah 16. Jumlah flip - flop dalam hal ini

adalah 4, karena 16 = 24. Pada baris yang sama, jumlah Flip-flop yang

diperlukan untuk membuat konter dengan nomor MOD 3, 6, 14, 28 dan 63 akan

menjadi 2, 3, 4, 5 dan 6 masing-masing. Secara umum, pengaturan jumlah minimum

N flip-flop dapat digunakan untuk membangun penghitung dengan modulus yang

diberikan oleh persamaan

2N −1 + 1 ≤ modulus ≤ 2N

2.Setelah itu tekan Run

Prinsip Kerja:

Saat input yang diberikan pada J dan K untuk JK flip-flop 1 berlogika 0, maka output pa Q akan berlogika 1 yang kemudian menjadi input pada jk flip flop 2, namun input dari clock tidak memberikan pengaruh pada keluaran di Q sehingga clock untuk JK flip flop 2,3, dan 4 tidak berfungsi sebagai clock karena tidak adanya perubahan logika.

Saat input yang diberikan pada J dan K untuk JK flip flop 1 berlogika 1, sesuai dengan karakteristik JK flip flop, saat clock juga memberikan input 1 maka logika pada Q adalah 1 atau dalam keadaan Latch, kemudian saat terjadi clock yang kedua maka output pada Q berubah menjadi 0 atau disebut togle, saat clock yang ketiga output Q akan kembali berubah menjadi 1 atau disebut togle. Dengan perubahan konstan pada output Q JK flip flop 1, yang kemudian menjadi input untuk clock JK flip flop 2. Prinsip yang sama terjadi berulang, namu membutuhkan waktu yang lebih lama untuk perubahan logika pada output Q di JKflip flop selanjutnya dikarenakan input clock pada JK flip flop keempat baru terjadi saat output Q JK flip flop sudah mengalami perubahan logika. Perubahan logika tersebut terjadi apabila clock pada JK flip flop 3 sudah mengalami perubahan logika, dan begitupun seterusnya. Maka banyak JK flip flop yang digunakan akan semakin lama waktu yang dibutuhkan untuk mendapatkan clock di output akhir. Pada rangkaian diatas, logika pada output berubah menjadi 1 pada saat clock ke 16. JK Flip Flop pertama yang mendapatkan input dari clock membutuhkan waktu 1 kali clock untuk mendapatkan clock pada Q, JK flip flop kedua membutuhkan 2 kali clock untuk mendapatkan clock pada output Q, JK flip flop ketiga membutuhkan 8 kali clock untuk mendapatkan clock pada output Q dan JK flip flop keempat membutuhkan 16 kali clock untuk mendapatkan clock pada output Q. Sehingga counter menghitung 1.

6. Link Download [back]

Materi - Download

Datasheet JK Flip - Flop - Download

File Html - Download

File Rangkaian Simulasi - Download

Video Rangkaian Simulasi - Download

No comments:

Post a Comment